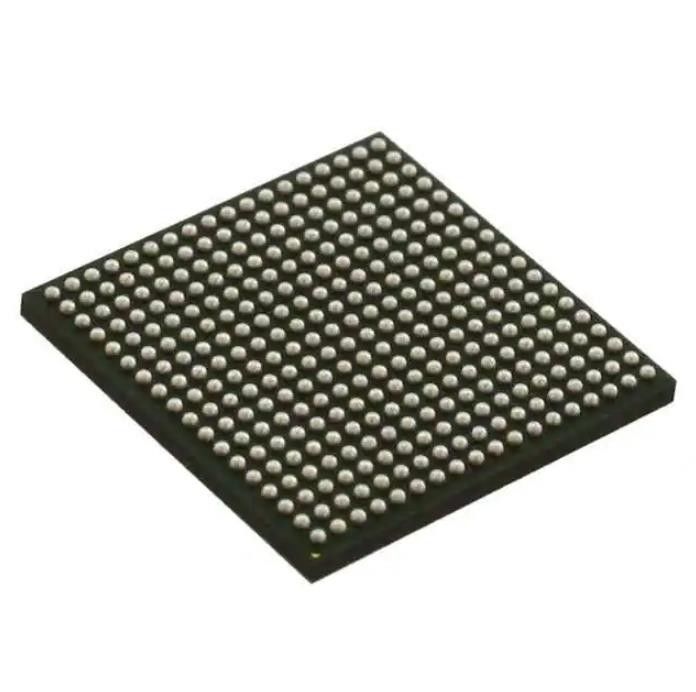

AM3352BZCZD80 Elektronische IC-Chips IC Mpu Sitara 800 MHz 324NFBGA

Produktdetails:

| Herkunftsort: | ursprünglich |

| Markenname: | original |

| Zertifizierung: | original |

| Modellnummer: | AM3352BZCZD80 |

Zahlung und Versand AGB:

| Min Bestellmenge: | 1 |

|---|---|

| Preis: | negotiation |

| Verpackung Informationen: | Kartonkasten |

| Lieferzeit: | Tage 1-3working |

| Zahlungsbedingungen: | T/T, L/C |

| Versorgungsmaterial-Fähigkeit: | 100.000 |

|

Detailinformationen |

|||

| Mfr: | Texas Instruments | Reihe: | Sitara™ |

|---|---|---|---|

| Paket: | Behälter | Produkt-Status: | Aktiv |

| Kern-Prozessor: | ARM® Cortex®-A8 | Zahl von Kernen/von Bus-Breite: | 1 Kern, 32-Bit |

| Geschwindigkeit: | 800MHz | Co-Processors/DSP: | Multimedia; NEON™ SIMD |

| Markieren: | AM3352BZCZD80,IC Mpu Sitara 800MHZ,Mpu Sitara 800MHZ 324NFBGA |

||

Produkt-Beschreibung

AM3352BZCZD80 Drahtloses HF-Modul IC Mpu Sitara 800 MHz 324 nfbga

ARM® Cortex®-A8 Mikroprozessor-IC Sitara™ 1 Kern, 32-Bit 800 MHz 324-NFBGA (15x15)

Spezifikationen von AM3352BZCZD80

| TYP | BESCHREIBUNG |

| Kategorie | Integrierte Schaltkreise (ICs) |

| Eingebettet | |

| Mikroprozessoren | |

| Hersteller | Texas Instruments |

| Serie | Sitara™ |

| Paket | Tablett |

| Produktstatus | Aktiv |

| Kernprozessor | ARM® Cortex®-A8 |

| Anzahl der Kerne/Busbreite | 1 Kern, 32-Bit |

| Geschwindigkeit | 800 MHz |

| Co-Prozessoren/DSP | Multimedia;NEON™ SIMD |

| RAM-Controller | LPDDR, DDR2, DDR3, DDR3L |

| Grafikbeschleunigung | Ja |

| Display- und Schnittstellencontroller | LCD, Touchscreen |

| Ethernet | 10/100/1000 Mbit/s (2) |

| SATA | - |

| USB | USB 2.0 + PHY (2) |

| Spannung – E/A | 1,8 V, 3,3 V |

| Betriebstemperatur | -40°C ~ 90°C (TJ) |

| Sicherheitsfunktionen | Kryptographie, Zufallszahlengenerator |

| Befestigungsart | Oberflächenmontage |

| Paket/Koffer | 324-LFBGA |

| Gerätepaket des Lieferanten | 324-NFBGA (15x15) |

| Zusätzliche Schnittstellen | CAN, I²C, McASP, McSPI, MMC/SD/SDIO, UART |

| Basisproduktnummer | AM3352 |

MerkmaleAM3352BZCZD80

• Bis zu 1 GHz Sitara™ ARM® Cortex® -A8 32-Bit-RISC-Prozessor

– NEON™ SIMD-Coprozessor

– 32 KB L1-Befehl und 32 KB Datencache mit Einzelfehlererkennung (Parität)

– 256 KB L2-Cache mit Fehlerkorrekturcode (ECC)

– 176 KB On-Chip-Boot-ROM

– 64 KB dedizierter RAM

– Emulation und Debug – JTAG

– Interrupt Controller (bis zu 128 Interrupt Requests)

• On-Chip-Speicher (gemeinsam genutzter L3-RAM)

– 64 KB OCMC-RAM (General-Purpose On-Chip Memory Controller).

– Zugänglich für alle Meister

– Unterstützt die Speicherung für schnelles Aufwachen

• Externe Speicherschnittstellen (EMIF)

– mDDR(LPDDR), DDR2, DDR3, DDR3L Controller:

– mDDR: 200-MHz-Takt (400-MHz-Datenrate)

– DDR2: 266-MHz-Takt (532-MHz-Datenrate)

– DDR3: 400-MHz-Takt (800-MHz-Datenrate)

– DDR3L: 400-MHz-Takt (800-MHz-Datenrate)

– 16-Bit-Datenbus

– 1 GB insgesamt adressierbarer Speicherplatz

– Unterstützt eine x16- oder zwei x8-Speichergerätekonfigurationen

– General-Purpose Memory Controller (GPMC)

– Flexible 8-Bit- und 16-Bit-asynchrone Speicherschnittstelle mit bis zu sieben Chip-Selects (NAND, NOR, Muxed-NOR, SRAM)

– Verwendet BCH-Code zur Unterstützung von 4-, 8- oder 16-Bit-ECC

– Verwendet Hamming-Code zur Unterstützung von 1-Bit ECC

– Fehlerortungsmodul (ELM)

– Wird in Verbindung mit dem GPMC verwendet, um Adressen von Datenfehlern aus Syndrompolynomen zu lokalisieren, die mithilfe eines BCH-Algorithmus generiert wurden

– Unterstützt 4-, 8- und 16-Bit-Fehlerortung pro 512-Byte-Block basierend auf BCH-Algorithmen

• Programmierbares Echtzeiteinheiten-Subsystem und industrielles Kommunikationssubsystem (PRU-ICSS)

– Unterstützt Protokolle wie EtherCAT®, PROFIBUS, PROFINET, EtherNet/IP™ und mehr

– Zwei programmierbare Echtzeiteinheiten (PRUs)

– 32-Bit-Lade-/Speicher-RISC-Prozessor mit einer Geschwindigkeit von 200 MHz

– 8 KB Befehls-RAM mit Einzelfehlererkennung (Parität)

– 8 KB Daten-RAM mit Einzelfehlererkennung (Parität)

– Einzelzyklus-32-Bit-Multiplikator mit 64-Bit-Akkumulator

– Verbessertes GPIO-Modul bietet ShiftIn/Out-Unterstützung und paralleles Latch für externe Signale

– 12 KB gemeinsam genutzter RAM mit Einzelfehlererkennung (Parität)

– Drei 120-Byte-Registerbänke, auf die jede PRU zugreifen kann

– Interrupt Controller (INTC) zur Verarbeitung von Systemeingabeereignissen

– Lokaler Verbindungsbus zum Verbinden interner und externer Master mit den Ressourcen innerhalb des PRU-ICSS

– Peripheriegeräte im PRU-ICSS:

– Ein UART-Port mit Flow-Control-Pins, unterstützt bis zu 12 Mbit/s

– Ein Enhanced Capture (eCAP)-Modul

– Zwei MII-Ethernet-Ports, die Industrial Ethernet wie EtherCAT unterstützen

– Ein MDIO-Port

• Power-, Reset- und Clock-Management-Modul (PRCM).

– Steuert den Ein- und Ausstieg in den Standby- und Tiefschlafmodus

– Verantwortlich für die Schlafsequenzierung, die Power-Domain-Ausschaltsequenzierung, die Wake-up-Sequenzierung und die Power-Domain-Einschaltsequenzierung

– Uhren

– Integrierter 15- bis 35-MHz-Hochfrequenzoszillator zur Erzeugung eines Referenztakts für verschiedene System- und Peripherietakte

– Unterstützt die individuelle Taktaktivierungs- und -deaktivierungssteuerung für Subsysteme und Peripheriegeräte, um den Stromverbrauch zu reduzieren

– Fünf ADPLLs zur Generierung von Systemtakten (MPU-Subsystem, DDR-Schnittstelle, USB und Peripheriegeräte [MMC und SD, UART, SPI, I 2C], L3, L4, Ethernet, GFX [SGX530], LCD-Pixeltakt)

AnwendungenvonAM3352BZCZD80

• Gaming-Peripheriegeräte

• Heim- und Industrieautomation

• Medizinische Verbrauchergeräte

• Drucker

• Intelligente Mautsysteme

• Angeschlossene Verkaufsautomaten

• Waagen

• Lernkonsolen

• Fortgeschrittenes Spielzeug

Umwelt- und Exportklassifizierungen vonAM3352BZCZD80

| ATTRIBUT | BESCHREIBUNG |

| RoHS-Status | ROHS3-konform |

| Feuchtigkeitsempfindlichkeitsniveau (MSL) | 3 (168 Stunden) |

| REACH-Status | REACH Unberührt |

| ECCN | 5A992C |

| HTSUS | 8542.31.0001 |

![]()

Möchten Sie mehr über dieses Produkt erfahren?