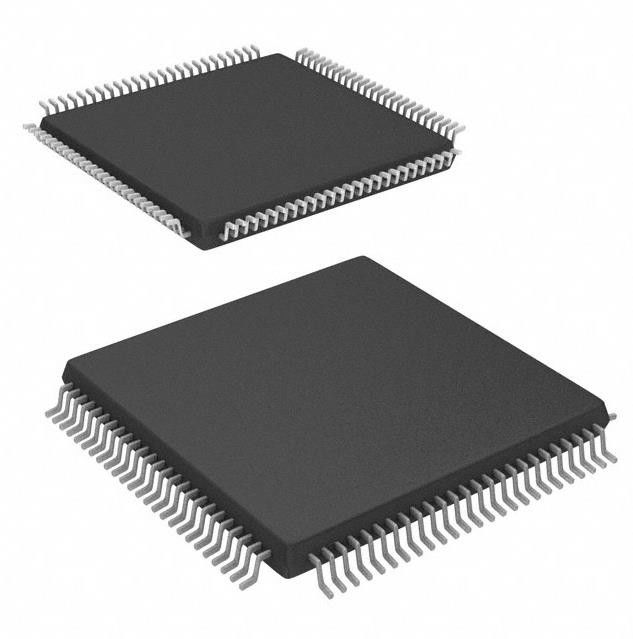

EPM3128ATC-10 N integrierte Schaltung Chip With CPLD 128MC 10NS 100TQFP

Produktdetails:

| Herkunftsort: | Vorlage |

| Markenname: | Original |

| Zertifizierung: | Original |

| Modellnummer: | EPM3128ATC-10 N |

Zahlung und Versand AGB:

| Min Bestellmenge: | 1 |

|---|---|

| Preis: | negotiation |

| Verpackung Informationen: | Karton-Kasten |

| Lieferzeit: | 3-4 Werktage |

| Zahlungsbedingungen: | T/T |

| Versorgungsmaterial-Fähigkeit: | 100 |

|

Detailinformationen |

|||

| Verzögerungs-Zeit tpd (1) maximal: | 10 ns | Spannungs-Versorgung - intern: | 3V | 3.6V |

|---|---|---|---|

| Zahl von Schaltelementen/von Blöcken: | 8 | Zahl von Macrocells: | 128 |

| Zahl von Toren: | 2500 | Zahl von Input/Output: | 80 |

| Markieren: | EPM3128ATC-10 N Chip integrierter Schaltung,Chip 100TQFP der integrierten Schaltung |

||

Produkt-Beschreibung

EPM3128ATC-10 N integrierte Schaltung Chip With CPLD 128MC 10NS 100TQFP

|

IC CPLD 128MC 10NS 100TQFP

|

Spezifikationen von EPM3128ATC-10 N

|

ART

|

BESCHREIBUNG

|

|

Kategorie

|

Integrierte Schaltungen (IC)

|

|

CPLDs (komplexe programmierbare Digitalbausteine)

|

|

|

Mfr

|

Intel

|

|

Reihe

|

MAX® 3000A

|

|

Paket

|

Behälter

|

|

Programmierbare Art

|

Im System programmierbar

|

|

Verzögerungs-Zeit tpd (1) maximal

|

10 ns

|

|

Spannungs-Versorgung - intern

|

3V | 3.6V

|

|

Zahl von Schaltelementen/von Blöcken

|

8

|

|

Zahl von Macrocells

|

128

|

|

Zahl von Toren

|

2500

|

|

Zahl von Input/Output

|

80

|

|

Betriebstemperatur

|

0°C | 70°C (TA)

|

|

Befestigung der Art

|

Oberflächenberg

|

|

Paket/Fall

|

100-TQFP

|

|

Lieferanten-Gerät-Paket

|

100-TQFP (14x14)

|

|

Niedrige Produkt-Zahl

|

EPM3128

|

Klima- u. Export-Klassifikationen von EPM3128ATC-10 N

| ATTRIBUT | BESCHREIBUNG |

| Feuchtigkeits-Empfindlichkeits-Niveau (MSL) | 3 (168 Stunden) |

| REICHWEITE Status | ERREICHEN Sie unberührtes |

| ECCN | EAR99 |

| HTSUS | 8542.39.0001 |

Eigenschaften von EPM3128ATC-10 N

■Leistungsstarke, preiswerte EEPROM-ansässige programmierbare Digitalbausteine CMOS (PLDs) errichteten auf einer MAX®-Architektur (sehen Sie Tabelle 1)

■Programmierbarkeit des Insystems 3.3-V (ISP) durch die eingebaute der Test-Aktionsgruppe IEEE Std. 1149,1 gemeinsame Schnittstelle (JTAG) mit moderner Stift-Blockierungsfähigkeit

– ISP-Schaltkreis konform mit IEEE Std. 1532

■Eingebauter Schaltkreis des Grenzescan-Tests (BST) konform mit IEEE Std. 1149.1-1990

■Erhöhte ISP-Eigenschaften:

– Erhöhter ISP-Algorithmus für schneller programmieren

– ISP_Done-Stückchen, zum der kompletten Programmierung sicherzustellen

– Pullup-Widerstand auf Input-/Outputstiften während der Insystemprogrammierung

■PLDs mit hoher Dichte, das von 600 bis 10.000 verwendbare Tore reicht

■4,5 ns-Stift-zustift-Logikverzögerungen mit Gegenfrequenzen von bis 227,3 MHZ

■MultiVoltTM Input-/Outputschnittstelle, dem Gerätkern zum Lauf bei 3,3 V ermöglichend, während Input-/Outputstifte mit logischen Zuständen 5.0-V, 3.3-V und 2.5-V kompatibel sind

■Pin-Zählungen, die von 44 bis 256 in einer Vielzahl des Flachgehäuses des dünnen Viererkabels reichen

(TQFP), Flachgehäuse des Plastikviererkabels (PQFP), Plastikj-führungschip-carrier (PLCC) und Feinlinien-BGATM-Pakete

■Heiße-socketing Unterstützung

■Programmierbare ununterbrochene Verlegungsstruktur der Verbindungsreihe (PIA) für schnelle, vorhersagbare Leistung

■Programmierbarkeit des Insystems 3.3-V (ISP) durch die eingebaute der Test-Aktionsgruppe IEEE Std. 1149,1 gemeinsame Schnittstelle (JTAG) mit moderner Stift-Blockierungsfähigkeit

– ISP-Schaltkreis konform mit IEEE Std. 1532

■Eingebauter Schaltkreis des Grenzescan-Tests (BST) konform mit IEEE Std. 1149.1-1990

■Erhöhte ISP-Eigenschaften:

– Erhöhter ISP-Algorithmus für schneller programmieren

– ISP_Done-Stückchen, zum der kompletten Programmierung sicherzustellen

– Pullup-Widerstand auf Input-/Outputstiften während der Insystemprogrammierung

■PLDs mit hoher Dichte, das von 600 bis 10.000 verwendbare Tore reicht

■4,5 ns-Stift-zustift-Logikverzögerungen mit Gegenfrequenzen von bis 227,3 MHZ

■MultiVoltTM Input-/Outputschnittstelle, dem Gerätkern zum Lauf bei 3,3 V ermöglichend, während Input-/Outputstifte mit logischen Zuständen 5.0-V, 3.3-V und 2.5-V kompatibel sind

■Pin-Zählungen, die von 44 bis 256 in einer Vielzahl des Flachgehäuses des dünnen Viererkabels reichen

(TQFP), Flachgehäuse des Plastikviererkabels (PQFP), Plastikj-führungschip-carrier (PLCC) und Feinlinien-BGATM-Pakete

■Heiße-socketing Unterstützung

■Programmierbare ununterbrochene Verlegungsstruktur der Verbindungsreihe (PIA) für schnelle, vorhersagbare Leistung

■PCI kompatibel

■Bus-freundliche Architektur einschließlich programmierbare Durchlauf-klassige Steuerung

■Offen-Abflussertragwahl

■Programmierbare macrocell Purzelbäume mit einzelnem klarem, eingestellt, Uhr und Uhr ermöglichen Kontrollen

■Programmierbarer Stromsparmodus für eine Leistungsreduzierung von vorbei 50% in jedem macrocell

■Konfigurierbare Expanderproduktausdruckverteilung, bis 32 Produktausdrücke pro macrocell erlaubend

■Programmierbares Sicherheitsstückchen für Schutz von eigenen Entwürfen

■Erhöhte Architektureigenschaften, einschließlich:

– Stift- 6 oder 10 oder Logik-gesteuerterertrag Freigabesignale

– Zwei globale Taktsignale mit optionaler Umstellung

– Erhöhte Verbindungsbetriebsmittel für verbessertes routability

– Durchlauf-klassige Steuerung des programmierbaren Ertrages

■Software-Entwurfsunterstützung und automatischer Platz-undweg bereitgestellt Alteras von den Entwicklungssystemen für Windows-basierte PC und Sun

SPARCstations und HP 9000 Reihe 700/800 Arbeitsplätze

■Zusätzlicher Entwurfseintritt und Simulationsunterstützung stellten von EDIF 2 0 0 und 3 0 0 netlist Dateien, Bibliothek von parameterisierten Modulen (LPM) zur Verfügung,

Verilog HDL, VHDL und andere Schnittstellen zu populären EDA-Werkzeugen von den Fremdherstellern wie Rhythmus, Exemplar-Logik, Mentor

Grafiken, OrCAD, Synopsys, Synplicity und VeriBest

■Programmierungsunterstützung mit der Vorlagenprogrammiereinheit Altera (MPU), MasterBlasterTM-Kommunikationen verkabeln, ByteBlasterMVTM

Downloadkabel der parallelen Schnittstelle, Seriendownloadkabel BitBlasterTM sowie Programmierungs-Hardware von den Fremdherstellern und

irgendeine schaltungsintern Prüfvorrichtung, die Standardtest JamTM und Dateien der Programmiersprache-(STAPL) (.jam) stützt, Byte-Code des Stau-STAPL

Dateien (.jbc) oder Serienvektor-Format-Dateien (.svf)

■Bus-freundliche Architektur einschließlich programmierbare Durchlauf-klassige Steuerung

■Offen-Abflussertragwahl

■Programmierbare macrocell Purzelbäume mit einzelnem klarem, eingestellt, Uhr und Uhr ermöglichen Kontrollen

■Programmierbarer Stromsparmodus für eine Leistungsreduzierung von vorbei 50% in jedem macrocell

■Konfigurierbare Expanderproduktausdruckverteilung, bis 32 Produktausdrücke pro macrocell erlaubend

■Programmierbares Sicherheitsstückchen für Schutz von eigenen Entwürfen

■Erhöhte Architektureigenschaften, einschließlich:

– Stift- 6 oder 10 oder Logik-gesteuerterertrag Freigabesignale

– Zwei globale Taktsignale mit optionaler Umstellung

– Erhöhte Verbindungsbetriebsmittel für verbessertes routability

– Durchlauf-klassige Steuerung des programmierbaren Ertrages

■Software-Entwurfsunterstützung und automatischer Platz-undweg bereitgestellt Alteras von den Entwicklungssystemen für Windows-basierte PC und Sun

SPARCstations und HP 9000 Reihe 700/800 Arbeitsplätze

■Zusätzlicher Entwurfseintritt und Simulationsunterstützung stellten von EDIF 2 0 0 und 3 0 0 netlist Dateien, Bibliothek von parameterisierten Modulen (LPM) zur Verfügung,

Verilog HDL, VHDL und andere Schnittstellen zu populären EDA-Werkzeugen von den Fremdherstellern wie Rhythmus, Exemplar-Logik, Mentor

Grafiken, OrCAD, Synopsys, Synplicity und VeriBest

■Programmierungsunterstützung mit der Vorlagenprogrammiereinheit Altera (MPU), MasterBlasterTM-Kommunikationen verkabeln, ByteBlasterMVTM

Downloadkabel der parallelen Schnittstelle, Seriendownloadkabel BitBlasterTM sowie Programmierungs-Hardware von den Fremdherstellern und

irgendeine schaltungsintern Prüfvorrichtung, die Standardtest JamTM und Dateien der Programmiersprache-(STAPL) (.jam) stützt, Byte-Code des Stau-STAPL

Dateien (.jbc) oder Serienvektor-Format-Dateien (.svf)

Verwandte Produkte

EPM3032A

EPM3064A

|

IC CPLD 128MC 10NS 100TQFP

|

Möchten Sie mehr über dieses Produkt erfahren?